Test III

Ülesanne

Praktikumi ülesandeks on nutikas süsteem, millele tuleb luua minimaalne juhtloogika VHDL keeles. Ülesandes on antud sisendid ning väljundid, kuid väljundfunktsioon tuleb meeskondadel endal koostada lähtudes ülesande tingimustest. Töö kord paneb paika nõutud sammud ülesande lahendamiseks. Loodud lahendust tuleb suuliselt kaitsta vastavas praktikumitunnis (11. või 12. tund). Kaitsmisel tuleb ettenäidata töötav simulatsioon ning laadida lahendus ka FPGAle. Ülesande kaitsmisel peab olema meeskonnal vähemalt ettenäidata põhjendatud väljundfunktsioonide tabel, parem oleks kui on koostatud ka aruanne. Ilma sisuliselt põhjendatud väljundfunktsioonide tabelita ülesannet kaitsta ei saa! Väljundfunktsioonide koostamisel ning ülesande mõistmisel on meeskonnale antud vabad käed, kuid pakutud lahendus peab olema põhjendatud. Näiteks kodus vannitoas ei ole vaja koguaeg väljatõmbe ventilaatorit järgi hoida, ühissaunas seevastu on see rohkem põhjendatud.

Soovituslik töö kord

- Kodeerida sisendid ja väljundid, mõne sisendi-väljundi puhul ei piisa ühest bitist!

- Määrata ülesande väljundfunktsioonid (põhjendatud!) lähtudes tingimustest

- Koostada tõeväärtustabel vastavalt punktile 1 ning minimeerida Espressoga kasutades -Dopoall käsku ning valides väikseima “totali”

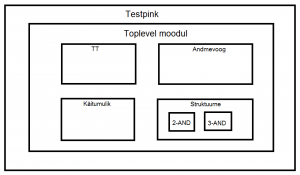

- Programmeerida korralikult kommenteeritud lahendus VHDLis, kus oleks järgmised komponendid (iga komponent eraldi failis k.a. struktuurne kirjeldusstiil, Joonis 1):

- toplevel moodul – hõlmab endas järgnevaid alamkomponente, v.a. testpink

- esialgne tõeväärtustabel

- andmevoo kirjeldustiilis Espresso lahendus

- käitumuslikus kirjeldusstiilis Espresso lahendus

- struktuurses kirjeldusstiilis Espresso lahendus (iga ventiil (gate) eraldi komponendina)

- 2-AND

- 3-AND jne.

- testpink – testib kõiki komponente samaaegselt

- toplevel moodul – hõlmab endas järgnevaid alamkomponente, v.a. testpink

- Veenduda simulatsiooniga korrektses lahenduses

- Aruande koostamine

- Lahenduse kaitsmine – praktikumitunnis simulatsiooni ettenäitamine + FPGAle laadimine

- Aruande esitamine

Aruanne

Aruanne peab olema vormistatud .pdf formaadis ning saadetud hiljemalt 11. teema-nädala lõpuks ehk 25. novembriks emailile hardi.selg[at]ati.ttu.ee. Meeskonna kohta tuleb esitada üks aruanne. Aruande aluseks võtta IT teaduskonna lõputöö vormistamise mall, kus peab sisalduma järgnev:

- Tiitelleht

- Annotatsioon – lühikokkuvõtte tööst. Annotatsiooni koostamine.

- Sisukord

- Sissejuhatus

- Töö sisu

- Lähteülesanne

- Põhjendatud väljundfunktsioonid

- Minimaalne espresso tulemus (selgitatud ekraanitõmmisega)

- VHDL programmi olulised, kommenteeritud lõigud (VHDL koodi tuim kopeerimine = 0 punkti aruande eest)

- Töös esinenud rasked kohad, probleemid jms.

- Kokkuvõte

- Kasutatud kirjeldus – kõik mida ülesande lahedamiseks kasutati k.a. foorumid või videod VHDLi õppimiseks

- Lisad – täielik VHDL kood

Hindamine

Korrektselt lahendatud ülesande eest on võimalik saada kuni 15 punkti, kus 10 punkti on võimalik teenida suulise kaitsmisega (korrektselt töötava simulatsiooni põhjendamine ning 5 punkti õigeaegselt esitatud aruande eest. Kaitsmisel on võimalus ka lahendus FPGAle laadida. Rangelt soovituslik on see IALB ning IASB õppekavade tudengitele.