Last modified: 2017-11-13 18:12:50

ALU disain ja süntees

ALU ehk aritmeetika-loogika seade on tuttav juba Arvutite ainest. Kellel asi meelest läinud, siis tasub meeles pidada vana tõde “kordamine on tarkuse ema”.

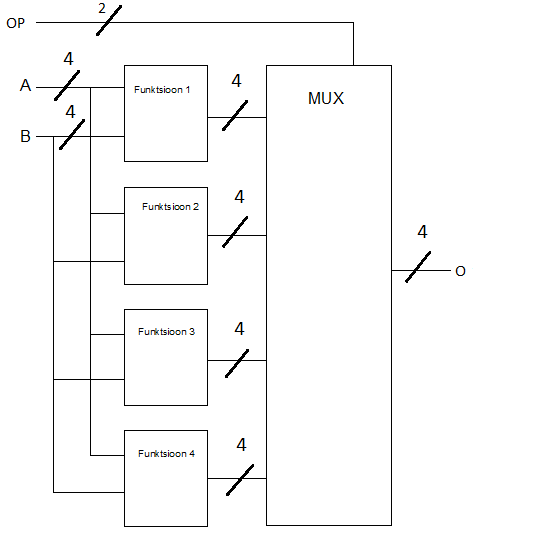

Antud praktikumi eesmärgiks on iseseisvalt koostada VHDL keeles nelja operatsiooni teostav ning neljabitiseid arve töötlev ALU. Joonisel 1 on ALU struktuurskeem. ALU operatsioonid on igale tudengile ettemääratud ning leiab siit.

Töö käik

- Mõista operatsioone, mida sinu ALU peab teostama. Iga operatsioon ei pruugi teostamiseks kasutada mõlemat sisendit (A ja B).

- Töö paremaks alustamiseks on eelnevalt juba valmis tehtud nii olem kui ka testpingi struktuur.

- Programmeeri ALU teostama vastavaid operatsioone.

- ALU peab olema programmeeritud struktuurselt (5 komponenti) nagu näidatud Joonisel 1.

- Funktsiooni 1 programmeerimisel võib kasutada teeki

std_logic_unsignedvõistd_logic_arith.

- Programmeeri testpink nii, et iga operatsioon saaks testitud. Ühtlasi võiks igal operatsioonil olla vähemalt 4 testi. Soovituslik on testida üks eriolukord (summeerides nulle) ja üks tavaline (2+2=4).

- Demonstreeri oma tulemust õppejõule = suuline kaitsmine.

- Koostada nõutud vormis aruanne, mis peab sisaldama sisulist selgitust ALU tööpõhimõttest ning teostatavatest operatsioonidest, koostatud ALU lähtekoodi ning simulatsioonipilti kõikide operatsioonide kohta.

- Koosta nõutud vormistuses aruanne, ning saada see õppejõule enne nõutud tähtaega!

- Tee tunni lõpus test:

- Esmaspäev 16.00

- Kolmapäev 8.15

Ülesannete kirjeldused

- Funktsioon 1

- A cmp B (võrdlustehe) – Sisendite võrdlemine. Kui A > B väljund 0010, kui A = B väljund 0000, kui A < B väljund 0001.

- A + B (aritmeetiline liitmine) – Sisendite A ja B summeerimine, ülekannet madalamast järgust ei ole ning lippu ületäitumise kohta ei ole vaja.

- A – B (aritmeetiline lahutamine) – Sisendi B lahutamine sisendist A. Lihtsuse huvides olgu A alati suurem kui B, mis tähendab, et laenulippu kasutada vaja ei ole.

- A, B cnt 1 – Sisenditest A ja B ühtede loendamine. Näiteks A = 1100 ja B = 0111, siis väljund = 5.

- A, B cnt 0 – Sisenditest A ja B nullide loendamine. Näiteks A = 1100 ja B = 0111, siis väljund = 3.

- Funktsioon 2

- shr A (nihe paremale) – Sisendi A nihutamine ühevõrra paremale ning vasakult tuleb sisse väärtus 0. Näiteks A = 0110 -> shr (A) = 0011.

- shl A (nihe vasakule) – Sisendi A nihutamine ühevõrra vasakule ning paremalt tuleb sisse väärtus 0. Näiteks A = 0110 -> shl (A) = 1100.

- rol A (ringnihe vasakule) – Sisendi A nihutamine ühevõrra vasakule ning paremalt tuleb sisse sisendi A kõige kõrgem bitt. Näiteks A = 1001 -> rol (A) = 0011.

- ror A (ringnihe paremale) – Sisendi A nihutamine ühevõrra paremale ning vasakult tuleb sisse sisendi A kõige madalam bit. Näiteks A = 1001 -> ror (A) = 1100.

- Funktsioon 3

- clr A, B (seada sõna A B-nda biti väärtuseks ‘0’) – Sisend B saab omada väärtusi (xx tähistab, et vastavate bittide väärtus meid ei huvita) xx00, xx01, xx10, xx11, mis määravad ära, mitmes bitt A-st keeratakse nulliks. Näiteks A = 1111, B = xx10 (kümnendkoodis 2, ehk siis kolmas bitt), clr A, B = 1011.

- set A, B (seada sõna A B-nda biti väärtuseks ‘1’) – Sisend B saab omada väärtusi (xx tähistab, et vastavate bittide väärtus meid ei huvita) xx00, xx01, xx10, xx11, mis määravad ära, mitmes bitt A-st keeratakse üheks. Näiteks A = 0000, B = xx11 (kümnendkoodis 3, ehk siis neljas bitt), set A, B = 1000.

- xor A, B (inverteerida sõna A B-nda biti väärtus) – Sisend B saab omada väärtusi (xx tähistab, et vastavate bittide väärtus meid ei huvita) xx00, xx01, xx10, xx11, mis määravad ära, mitmes bitt A-st keeratakse ümber. Näiteks A = 0110, B = xx01 (kümnendkoodis 1, ehk siis teine bitt inverteeritakse), xor A, B = 0100.

- Funktsioon 4

- Kõik tehted on loogikatehted.

- Enda matrikkli numbrile vastava ülesande leiad SIIT!

FPGA süntees

Alates sügisest 2016 on üles seatud FPGAl baseeruv kauglabor (kolledži tudengi diplomitöö). Kauglabori eesmärk on anda tudengitele võimalus programmeeritud VHDL koodi ka sünteesida ning laadida FPGAle. Juhitav FPGA arenduskomplekt on Digilent Nexys 3. Koodi sünteesimiseks tuleb:

- Laadida oma arvutisse Xilinx ISE 14.7 WebPack programm

- Avada meie pakutud näidis projekt Xilinx ISE programminga ning lisada/muuta programm eelnevalt loodud koodiga

- Uurida programmi kasutusjuhendit, kompileerida kood ning teha “Generate programming file”

- Leida projektikataloogist “.bit” lõpuga fail ning laadida kauglabori keskkonda

- Registreeruda aadressil playground.itcollege.ee, määrata omale aeg ning laadida .bit fail keskkonnas

- Emuleerida nuppude vajutamist ning veenduda, et sünteesitud kood töötab FPGAl õigesti

Vastuseid küsimustele, et mis on FPGA leiab nii Googlest kui ka Youtube keskkonnast. Üks video, kus võrreldakse mikrokontrollerit ning FPGAd.