Last modified: 2020-05-25 13:51:28

Oluline

- Praktikumi aruandeid medadvice.netvõetakse vastu, kuni TUDENGI ENDA EKSAMINI. Ehk kui tudeng registreerus eksamile 10. найти работу в сочи jaanuar, siis praktikumide aruanded tuleb saata hiljemalt 9. jaanuari keskööks.

- 2016 aasta päevaõppe videoloengud, kaugõppe videoloengud.

Motivatsioon

Tutvustada ühte võimalikku lähenemist eriotstarvelise riistvara disainimiseks kasutades selleks VHDL-keele simulatsiooni. Praktikumide raames on võimalik kasutada FPGA kauglaborit koodi sünteesimiseks, mis on loogiline samm eriotstarbelise riistvara loomisel. Praktilised VHDLi ülesanded heidavad pilgu, kuidas andmeid riistvara tasemel töödeldakse. Samuti luuakse ka seos kõrgema abstratksioonitaseme kirjeldusega.

Praktikumi tunnid

Praktikumideks on tunniplaanis ette nähtud 2 kontakttundi, mille jooksul tutvustatakse digitaalsüsteemide programmeerimist VHDL keeles. Praktikumide tundide sisu sügisel 2017 on jaotatud vastavalt Tabelile 1.

| # | Sisu |

|---|---|

| 1 | Praktiliste ülesannete tutvustus ja ZamiaCADis VHDL näiteülesande simuleerimine |

| 2 | Applettide tutvustus; VHDLi ülesannete lahendamise abistamine ja test |

Praktikumide kord

Praktikumide arvestuse saamiseks peab tudeng kinni pidama praktikumide korrast. Kui mõni punkt jääb ebaselgeks kirjutada õppejõule või küsida tunnis.

- Praktikumide ülesannete tulemused tuleb esitada kirjalikult aruande vormis. Esitada tuleb üks aruanne mõlema ülesande kohta.

- Praktikumi ülesande aruannete nõuded on eraldi väljatoodud.

- Ülesannete lahenduskoodid lisada aruandele eraldi! Koodiga aruanne kuulub ümbertegemisele. Aruande ilmestamiseks võib aruandesse panna vaid iseloodud ning korralikult lahtiseletatud olulisimad koodiread.

- Praktikumide tulemusi võetakse vastu kuni eksamini.

- Praktikumide tulemused hinnatakse pärast eksamit, olenemata saatmise ajast, kui kõik tööd on saadetud!

- Aruannete koostamisel võib lähtuda etteantud mallist:

- Ilma mõjuva ning etteteatatud põhjuseta hilinenud aruande eest punkte ei saa.

- Aruanded esitatakse üks kord, kui õppejõud pole nõudnud aruande parandamist.

- Õppejõul on õigus aruande kohta esitada tudengile täiendavaid küsimusi.

- Aruanded tuleb esitada emaili teel aadressile: priit.ruberg[ät]itcollege.ee

- Aruanded saata PDF formaadis.

- Lisaeksamit sooritavad tudengid võivad praktikume uuesti sooritada. Viimane toimub koos eelneva teatamisega praktikumide õppejõule.

- Eelnevalt sooritatud praktikumide punkte on võimalik ülekanda, kuid seda läbirääkimiste teel praktikumi õppejõuga.

- Kellegi teise töö esitamine ilma viitamiseta on plagiaat!

Praktikumides osalemisega oled nõustunud sellest korrast kinni pidada!

Hindamine

Praktikumide eest on võimalik saada kuni 30 punkti, mis on ühtlasi osa aine lõpphindest. Praktikumide tundidest osavõtt on rangelt soovituslik.

Praktikumide punktid jagunevad järgmiselt:

| # | Teema | Kommentaar punktide jagunemise kohta | Max. punktid |

|---|---|---|---|

| 1 | MUX ülesanne | 2-kirjeldusstiili kohta (3), 2-testpink | 8 |

| 2 | ALU ülesanne | 2x komponent (4), 2-testpink,2- mux, FPGA süntees+5 | 12(17) |

| 3 | Test | selgitus allpool | 10 |

FPGA süntees

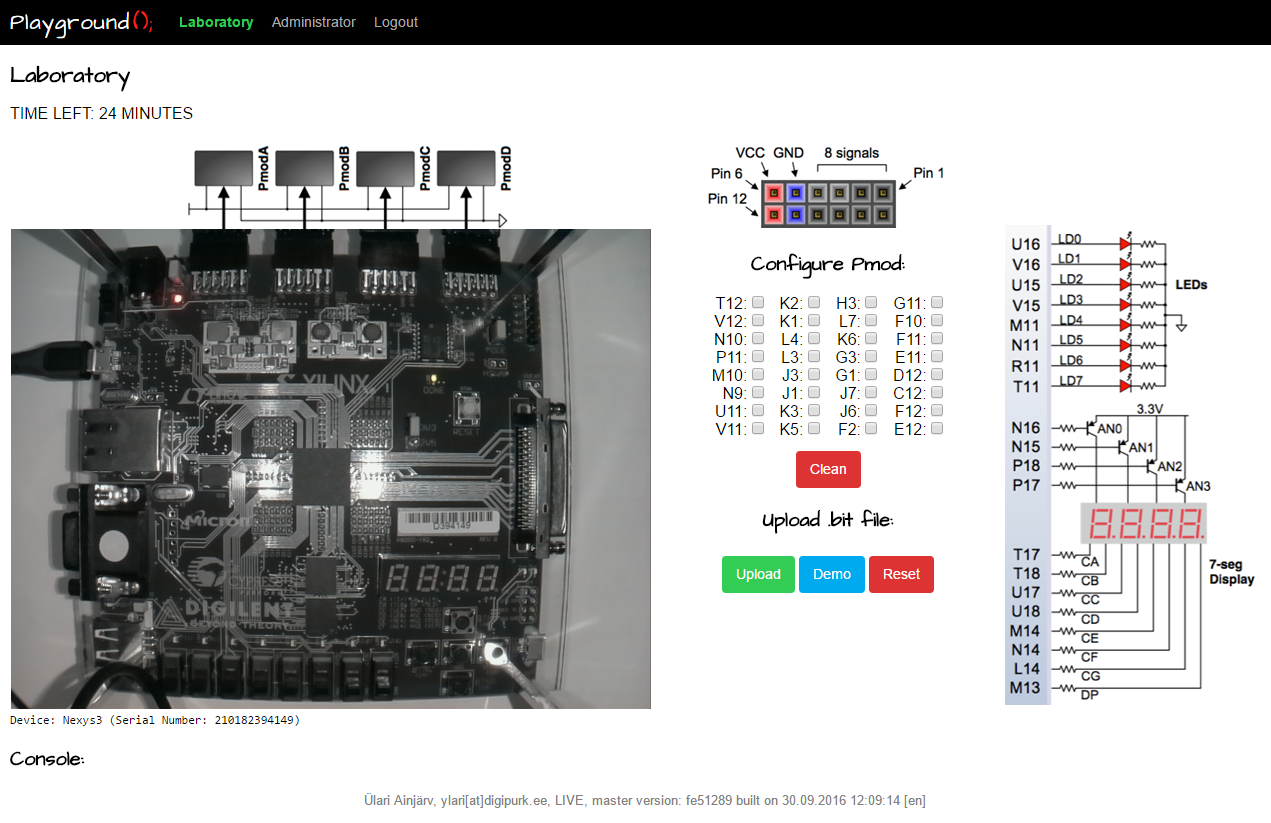

Alates sügisest 2016 on üles seatud FPGAl baseeruv kauglabor (kolledži tudengi diplomitöö). Kauglabori eesmärk on anda tudengitele võimalus programmeeritud VHDL koodi ka sünteesida ning laadida FPGAle. Juhitav FPGA arenduskomplekt on Digilent Nexys 3. Koodi sünteesimiseks tuleb:

- Laadida oma arvutisse Xilinx ISE 14.7 WebPack programm

- Avada meie pakutud näidis projekt Xilinx ISE programminga ning lisada/muuta programm eelnevalt loodud koodiga

- Uurida programmi kasutusjuhendit, kompileerida kood ning teha “Generate programming file”

- Leida projektikataloogist “.bit” lõpuga fail ning laadida kauglabori keskkonda

- Registreeruda aadressil playground.itcollege.ee, määrata omale aeg ning laadida .bit fail keskkonnas

- Emuleerida nuppude vajutamist ning veenduda, et sünteesitud kood töötab FPGAl õigesti

Vastuseid küsimustele, et mis on FPGA leiab nii Googlest kui ka Youtube keskkonnast. Üks video, kus võrreldakse mikrokontrollerit ning FPGAd.

FPGA kauglabori vaade

Tulemused

Kaugõppe tulemused kuvatakse eraldi aine praktikumide lehel.

Aruanne

Aruanne peavad olema vormistatud .pdf formaadis ning saadetud enne eksamit emailile priit.ruberg[at]itcollege.ee. Meeskonna kohta tuleb esitada üks aruanne. Aruande aluseks võtta Praktikumide korras pakutud mall, kus peab sisalduma järgnev:

- Tiitelleht

- Annotatsioon – lühikokkuvõtte tööst. Annotatsiooni koostamine.

- Sisukord

- Sissejuhatus

- Töö sisu (oleneb ülesandest)

- Lähteülesanne, põhjendatud väljundfunktsioonid, minimaalne espresso tulemus (lisatud kommenteeritud ekraanitõmmis)

- VHDL programmi olulised, lahtiseletatud ning kommenteeritud lõigud (VHDL koodi tuim kopeerimine = 0 punkti aruande eest)

- Töös esinenud rasked kohad, probleemid jms.

- Meeskonna töö puhul ülesannete ning koormuse jaotus meeskonna liikmete vahel

- Kokkuvõte

- Kasutatud kirjeldus – kõik mida ülesande lahedamiseks kasutati k.a. foorumid või videod VHDLi õppimiseks

- Lisad, kui on

Test

Teises praktikumitunnis toimub avatud materjalidega, kuid ajalimiidiga test, mis koosneb kuni 20 küsimusest ning annab kuni 10 punkti. Küsimused baseeruvad selleks ajaks läbitud loengute ning praktikumide materjalidel. Test hõlmab endas nii teoreetilisi küsimusi, kui ka praktilisi ülesandeid. Testis on üldisi küsimusi riistvarakirjelduskeele VHDL kohta. Test koosneb kahest osast. Test sooritatakse II praktikumitunni lõpus, 9. detsembril 2017. Ilma eelneva etteteatamiseta testi järeleteha ei saa. Test on ajapiiranguga 15-20 minutit. Testi tulemused avaldatakse kohe testi lõppedes. Test tuleb sooritada olles füüsiliselt kohal praktikumitunnis.