Last modified: 2017-10-30 11:01:46

Test II

Meeskonnatöö ülesanne

Praktikumi ülesandeks on nutikas süsteem, millele tuleb luua minimaalne juhtloogika VHDL keeles. Ülesandes on antud sisendid ning väljundid, kuid väljundfunktsioon tuleb meeskondadel endal koostada lähtudes ülesande tingimustest. Töö kord paneb paika nõutud sammud ülesande lahendamiseks. Loodud lahendust tuleb suuliselt kaitsta vastavas praktikumitunnis (7. või 8. tund). Kaitsmisel tuleb ettenäidata töötav simulatsioon, mille kohta õppejõul on õigus juurde küsida. Lisaks on sellel aastal võimalus laadida lahendus ka kauglaborina töötavale FPGAle, mis on kolledži tudengi lõputööna valminud. FPGAle laadimise eelduseks on Xilinx ISE programmiga edukalt sünteesitud .bit faili loomine.

Ülesande kaitsmisel peab olema meeskonnal vähemalt ettenäidata põhjendatud väljundfunktsioonide tabel, parem oleks kui on koostatud ka aruanne. Ilma sisuliselt põhjendatud väljundfunktsioonide tabelita ülesannet kaitsta ei saa! Väljundfunktsioonide koostamisel ning ülesande mõistmisel on meeskonnale antud vabad käed, kuid pakutud lahendus peab olema põhjendatud. Näiteks kodus vannitoas ei ole vaja koguaeg väljatõmbe ventilaatorit järgi hoida, ühissaunas seevastu on see rohkem põhjendatud.

Soovituslik töö kord

- Määrata ülesande väljundfunktsioonid (põhjendatud!) lähtudes tingimustest

- Koostada tõeväärtustabel vastavalt punktile 1 ning minimeerida Espressoga kasutades -Dopoall käsku ning valides väikseima “totali”

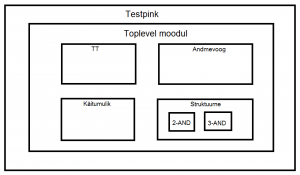

- Programmeerida korralikult kommenteeritud lahendus VHDLis, kus oleks järgmised komponendid (iga komponent eraldi failis k.a. struktuurne kirjeldusstiil, Joonis 1):

- toplevel moodul – hõlmab endas järgnevaid alamkomponente, v.a. testpink

- esialgne tõeväärtustabel

- andmevoo kirjeldustiilis Espresso lahendus

- käitumuslikus kirjeldusstiilis Espresso lahendus

- struktuurses kirjeldusstiilis Espresso lahendus (iga ventiil (gate) eraldi komponendina)

- 2-AND

- 3-AND jne.

- testpink – testib kõiki komponente samaaegselt, testimist sooritatakse mitme testkomplektiga

- toplevel moodul – hõlmab endas järgnevaid alamkomponente, v.a. testpink

- Veenduda simulatsiooniga korrektses lahenduses

- Aruande koostamine

- Lahenduse kaitsmine – praktikumitunnis simulatsiooni ettenäitamine, võimalusel ka FPGAle laadimine

- Aruande esitamine

Aruanne

Aruanne peab olema vormistatud .pdf formaadis ning saadetud hiljemalt 1. detsembriks emailile priit.ruberg[at]itcollege.ee. Meeskonna kohta tuleb esitada üks aruanne. Aruande aluseks võtta Praktikumide korras pakutud mall, kus peab sisalduma järgnev:

- Tiitelleht

- Annotatsioon – lühikokkuvõtte tööst. Annotatsiooni koostamine.

- Sisukord

- Sissejuhatus

- Töö sisu

- Lähteülesanne

- Põhjendatud väljundfunktsioonid

- Minimaalne espresso tulemus (lisatud kommenteeritud ekraanitõmmis)

- VHDL programmi olulised, kommenteeritud lõigud (VHDL koodi tuim kopeerimine = 0 punkti aruande eest)

- Töös esinenud rasked kohad, probleemid jms.

- Kokkuvõte

- Kasutatud kirjeldus – kõik mida ülesande lahedamiseks kasutati k.a. foorumid või videod VHDLi õppimiseks

- Lisad – täielik VHDL kood

Hindamine

Korrektselt lahendatud ülesande eest on võimalik saada kuni 15 punkti (20 koos FPGA lahendusega), kus 10 punkti on võimalik teenida suulise kaitsmisega ning 5 punkti õigeaegselt esitatud aruande eest. Xilinx ISEs koostatud korretkne kood ning FPGAle laetud ekraanitõmmis annavad lisaks juurde 5 punkti.

FPGAle laadimine

- Lae alla Xilinx ISE Webpack 14.7 ning installeeri see

- Ava meiepoolt ettevalmistatud projekt Xilinx ISE programmis

- Tutvu Xilinx ISE programmi kasutusjuhendiga

- Kopeeri vabaltvalitud kirjeldusstiilis funktsionaalne kood ISEsse ning genereeri bitfail

- Mine lehele kauglabori lehele Playground(); ning registreeri kasutaja

- Vali omale sobiv kauglabori aeg

- Labori ajal lae oma .bit fail FPGAle ning veendu, et kood ka riistvaral korrektselt töötab

- Ära unusta FPGAle laetud programmist ka veebilehitsejast ekraanitõmmist teha